A frequency divider is a module that reduces the frequency of a signal.one2oneĬD4017 - A Decade Counter with Decoded Output Il i f Implementation of di it l f digital frequency di. 9 CLK Shift register, oscillator frequency FV : Comparator frequency divider stage output frequency FR : Reference frequency divider stage output frequency N : Setting for 14-bit programmable counter on comparator side … 4 VDD Power, for built-in charge pump 8 Pin Frequency divider input pin in comparator stage. Locking range enhancement of divide‐by‐two injection locked frequency … Shift Registors & Counters - Instrumentation Transducers … How To Implement Clock Divider in VHDL - Surf-VHDL

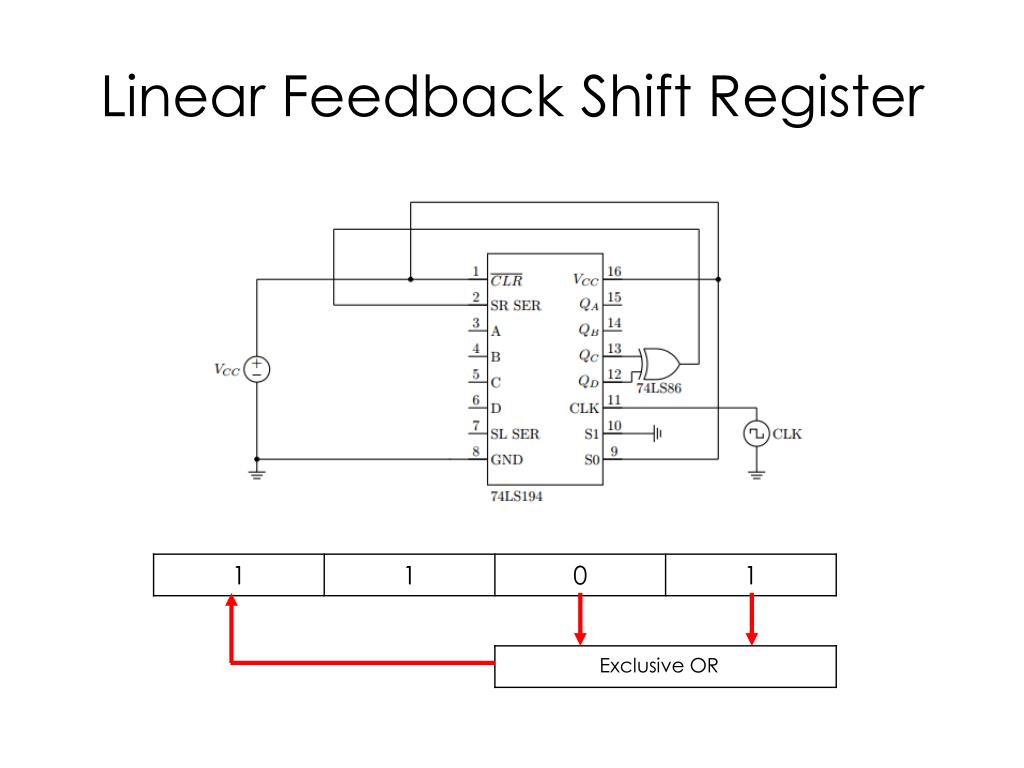

WebA digital frequency divider has a single circulating shifter register loaded with a bit … property management charge WebQuestion: Complete the three-bit shift register timing digran shown in Figure 8.1. That is, they either take in a bunch of bits singly and then output them all at once, or they take. Shift registers are most commonly used as serial-to-parallel or parallel-to-serial converters.Figure 4 todis torvaianica fotoĦ.8: Frequency Divider - Engineering LibreTexts shift register frequency divider meanĮLET3405 Lab3 FrequencyDividerRegister StudentManual.docx Web4. Record the states of LA through LD in the table under the column labeled Clear. T urn SW1 off, then on to reset all ß ip-ß ops. The circuit requires tw o inte grated circuit chips labeled IC1 and IC2. W ire the circuit as sho wn in Figure 5 with SW1 on (high) and X off (low). Shift register frequency divider mean Webdivider circuit. In this role they are very similar to the delay-line memory sy… to distinguish right from wrong definition By connecting the last flip-flop back to the first, the data can cycle within the shifters for extended periods, and in this form they were used as a form of computer memory. They share a single clock signal, which causes the data stored in the system to shift from one location to the next. Step …Ĭopy of Shift register frequency divider - Multisim LiveĪ shift register is a type of digital circuit using a cascade of flip-flops where the output of one flip-flop is connected to the input of the next. WebUsing the Intel® Quartus® Prime Timing Analyzer x. B = (clock cycles)*5592405 result = B/2^24 The size of B would depend the maximum size of clock cycles and can be computed by maximum register size for B = integer of ( (log10 ( (max size of clock cycles)*5592405)/log10 (2)) + 0.5) Share Improve this answer Follow After multiplying the clock cycles and 5592405, just divide by 2^24.Kubiatowicz (CS152) Digital Integrated Circuits 2/e …

0 kommentar(er)

0 kommentar(er)